2014/09/01_FPGAでdecorder組み合わせ回路

FPGA

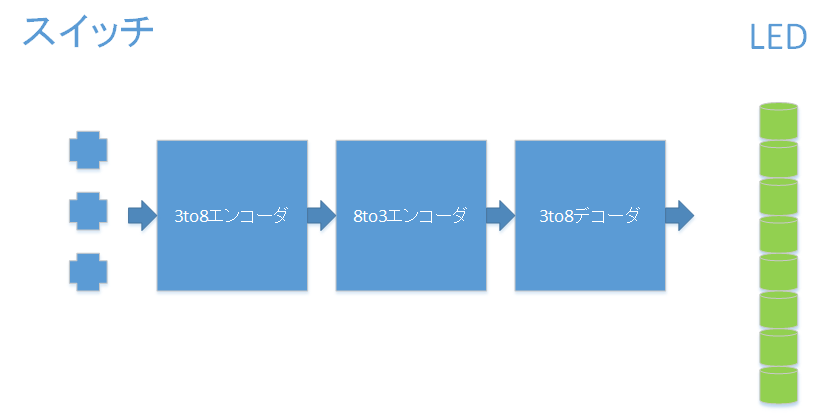

先程に引き続き、デコーダ+エンコーダ回路を作成。(先日と同じやつですが)

3to8デコーダの出力→8to3エンコーダ→3to8デコーダで結果をLEDに出力しています。

回路としては無意味なものですが、練習用にはちょうどよいです。

以下ソース

decorder_top.v

`timescale 1ns / 1ps

module decorder_top(

input [2:0] ssw,

output [7:0] led

);

wire [7:0] dec_;

wire [2:0] dout1;

wire [7:0] dout2;

decorder3to8 dec1(.din(ssw),.dout(dec_));

encorder8to3 enc (.din(dec_),.dout(dout1));

decorder3to8 dec2(.din(dout1),.dout(dout2));

assign led = dout2;

endmodule

decorder3to8.v

`timescale 1ns / 1ps

module decorder3to8(

input wire [2:0] din,

output reg [7:0] dout

);

always@(din)begin

case(din)

3'b000:dout <= 8'b00000001;

3'b001:dout <= 8'b00000010;

3'b010:dout <= 8'b00000100;

3'b011:dout <= 8'b00001000;

3'b100:dout <= 8'b00010000;

3'b101:dout <= 8'b00100000;

3'b110:dout <= 8'b01000000;

3'b111:dout <= 8'b10000000;

default: dout<=8'bxxxxxxxx;

endcase

end

endmodule

encorder8to3.v

`timescale 1ns / 1ps

module encorder8to3(

input wire [7:0] din,

output reg [2:0] dout

);

always@(din)begin

case(din)

8'b00000001:dout <= 3'b000;

8'b00000010:dout <= 3'b001;

8'b00000100:dout <= 3'b010;

8'b00001000:dout <= 3'b011;

8'b00010000:dout <= 3'b100;

8'b00100000:dout <= 3'b101;

8'b01000000:dout <= 3'b110;

8'b10000000:dout <= 3'b111;

default: dout <= 3'bxxx;

endcase

end

endmodule

decorder_top.ucf

NET "led(7)" LOC =N12; NET "led(6)" LOC =P16; NET "led(5)" LOC =D4; NET "led(4)" LOC =M13; NET "led(3)" LOC =L14; NET "led(2)" LOC =N14; NET "led(1)" LOC =M14; NET "led(0)" LOC =U18; NET "ssw(2)" LOC =C14; NET "ssw(1)" LOC =D14; NET "ssw(0)" LOC =A10;

このような感じです。

次は単一な回路でなく組み合わせ回路をつくりたいと思います。