Atlysのプロジェクトファイル,ソースファイルの作成と合成(Hello world! for VHDL )

ISEのインストールが完了したらプロジェクトファイルとソースファイルを作成します.

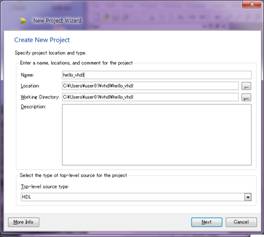

プロジェクトファイルの作成

ISEを立ち上げる.

Menu → File → New Project...

New Project Wizardが表示されたら

Nameを入力(例hello_vhdl)

[Next]クリック.

Project SettingsでAtlysの場合は次をセット.

Family → Spartan6

Device → XC6SLX45

Package → CSG324

[Next]クリック.

Projext Summryで

[Finish]クリック.

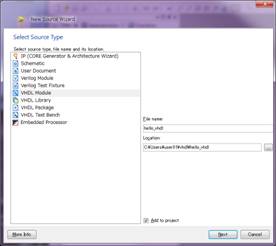

VHDLソースファイルの作成

Menu → Project → New Source

New Source Wizardが表示されるので

Select Soure Type で

File Name入力(例 hello_vhdl)

Select source type...で

VHDL Moduleを選ぶ

[Next]クリック

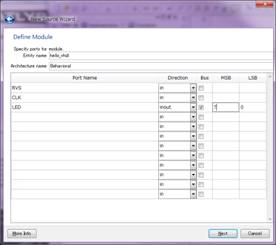

Define Moduleで

Port Nameを定義

RVS : in std_logic;

CLK : in std_logic;

LED : inout std_logic_vector(7 downto 0);

LEDはBusをチェックMSB→7 LEB→0

(後でISEエディタから変更もできる.)

[Next]クリック

Summary で[Finish]クリック

以上で*.vhdファイルのひな形ができます.

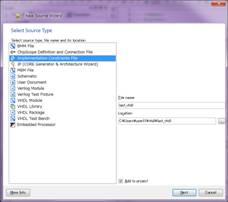

*.ucfファイルの作成

*.ucfファイルはデバイス間の接続などを定義します.

Menu → Project → New Source

New Source Wizardが表示されるので

Select Soure Type でFile Name入力(例 hello_vhdl)

Select source type...で

Implementation Constraints Fileを選ぶ

[Next]クリック

Summary で

[Finish]クリック

以上で*.ucfの空ファイルができます.

ここにISEエディタから次を入力し, [Ctrl]+[S]で保存します.

#FOR ATLYS

NET "RVS" LOC

= "F6"; #BTNR

NET "CLK" LOC

= "L15"; #GCLK

NET "LED<0>" LOC = "U18"; #LD0

NET "LED<1>" LOC = "M14"; #LD1

NET "LED<2>" LOC = "N14"; #LD2

NET "LED<3>" LOC = "L14"; #LD3

NET "LED<4>" LOC = "M13"; #LD4

NET "LED<5>" LOC = "D4"; #LD5

NET "LED<6>" LOC = "P16"; #LD6

NET "LED<7>" LOC = "N12"; #LD7

*.vhdファイルの編集

*.vhdファイルを開き,次のように編集し,[Ctrl]+[S]で保存します.

------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity hello_vhdl is

Port

(

RVS : in STD_LOGIC;

CLK : in STD_LOGIC;

LED : out STD_LOGIC_VECTOR

(7 downto 0)

);

end hello_vhdl;

architecture Behavioral of hello_vhdl is

signal

CNT :

std_logic_vector(33 downto 0);

begin

process(CLK)

begin

if

CLK'event and CLK='1' then

if

RVS='0' then

CNT<=CNT+1;

else

CNT<=CNT-1;

end

if;

LED<=CNT(33

downto 26);

end

if;

end

process;

end Behavioral;

-------------------------------------------------------------------

ISEの左下ペイン上の[Generate Programming File]を右クリック → Rerun ALL

以上で合成(Synthesize)が開始されます.

合成に成功すると作業フォルダ上に*.bitファイルが出来上がります.

C:\Users\user01\vhdl\hello_vhdl>dir *.bit [Enter]

ドライブ C のボリューム ラベルがありません。

ボリューム シリアル番号は C853-0953 です

C:\Users\user01\vhdl\hello_vhdl のディレクトリ

2012/08/01 14:45 1,484,500 hello_vhdl.bit

1 個のファイル 1,484,500 バイト

Atlys上での実行

(前提:Digilent Adeptのインストールが完了していること.)

Atlysの電源スイッチがOFFになっていること(ON表示の逆側)を確認してACアダプタを接続する.

AtlysをUSBでパソコンと接続する.

Atlysの電源スイッチをONにする.

Digilent Adeptを立て上げる.

[Browse...]ボタンをクリックしてISEで合成された*.bitファイルを選ぶ.

[Program]ボタンをクリックして,プログラムをAtlysにアップロードする.

アップロードが完了すると自動的にプログラムが開始される.

プログラムは,LEDを8ビットカウンタに見立てて点灯消灯を繰り返す.