FPGAをはじめる

FPGA(Field Programmable Gate Array)は書き換えが可能であることが最大の特徴でハードウェア言語HDLで内部回路の記述をおこないます。

製品開発では大量生産のしやすいASICを用いるのが一般的ですが一度書き込むと回路の変更ができないため学習には向いていません。

その点FPGAは書き換えが可能なのでHDLや論理回路の学習に役立つのではないかと思います。

FPGA開発に必要なもの

FPGA開発に当たって必要なものは- FPGA搭載ボード

- FPGA用統合開発環境

この二つです。FPGAには種類がたくさんあります。さらにそれを搭載した評価ボードも何種類もあります。

FPGAは主流なものとしてXilinx社製とAltera社製があり、どこ製のFPGAを使用するかで開発環境は変わってくるので気をつけてください。

ここではXilinx社製のFPGAを搭載したDigilent社製の評価ボードを使用して説明していきます。

改めて用意するものはこちらです。

- Atlys

- ISE Design Suite 14.4

ISE Design SuiteがあればXilinx社製FPGAを搭載したボードは同様に開発できます。

ISEのインストール

まずは開発環境をインストールします。Xilinx Xilinx社のISEWebPACKダウンロードのページからISEをダウンロードします。

ダウンロードにはXilinxのアカウント登録が必要になるので登録してダウンロードしてください。

FPGAの開発

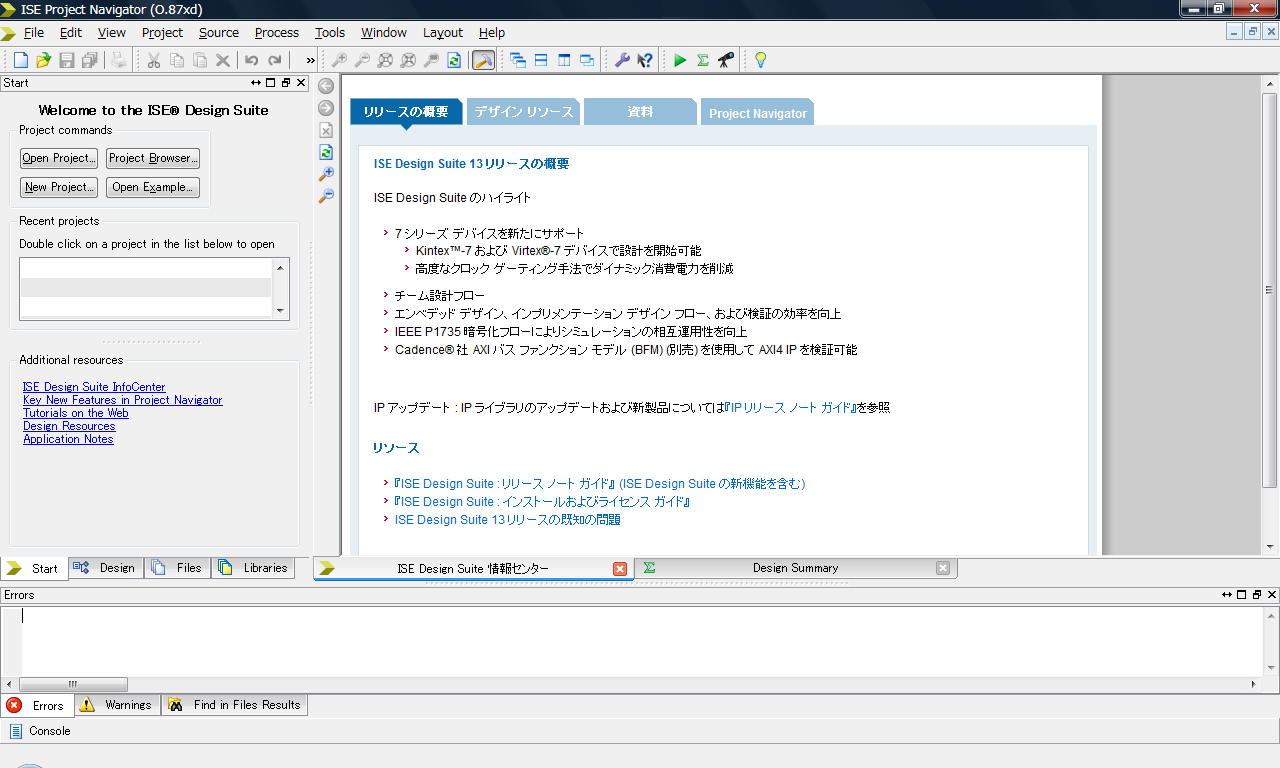

開発の手順を説明していきます。 はじめにISEを起動します。 起動するとスタート画面になるのでメニューから[File]→[NewProject]を選択しプロジェクトを作成します。

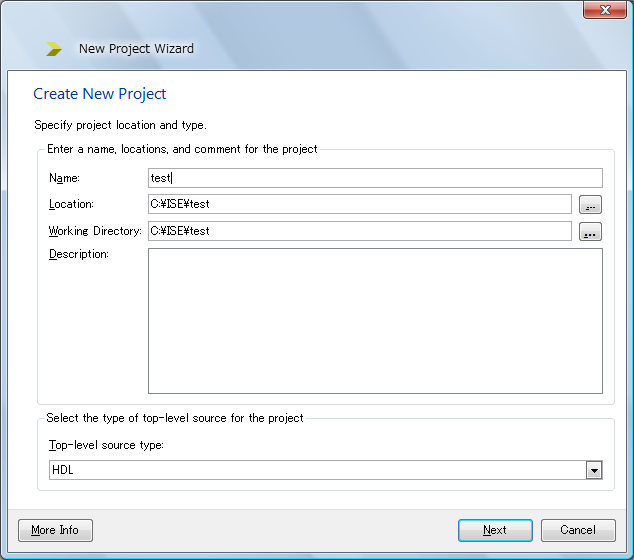

プロジェクトウィザードが起動するのでプロジェクト名を設定して[Next]を押します。

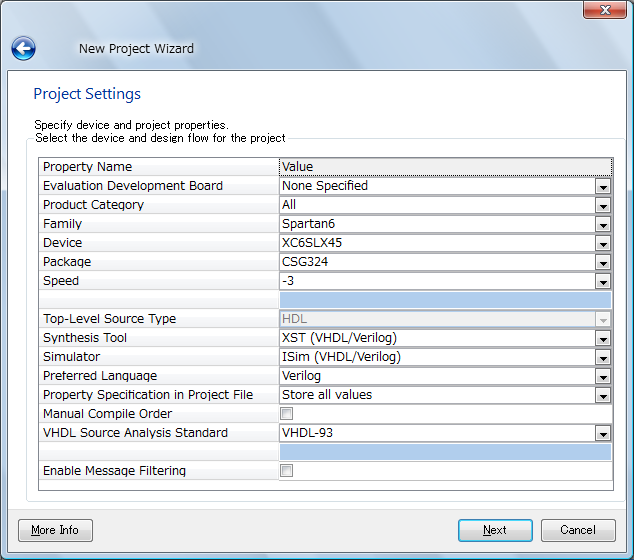

デバイスの設定画面に移るので使用しているFPGAの種類を入力します。手元のボードがAtlysでないは場合仕様書を読んでFPGAの種類を確認してください。

[Family] [Device] [Package] を該当するものに変更します。

また、今回は言語としてVerilogを使用するので[Preterred Language]をVerilogに変更します。

変更したら[Next]を押します。

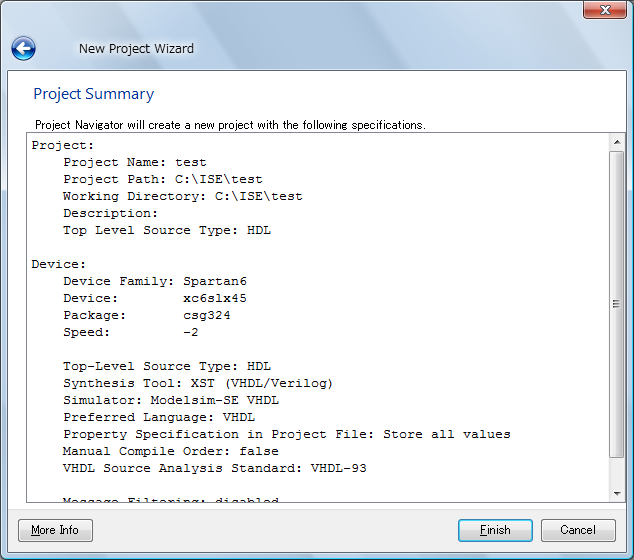

設定の確認なので[Finish]を押してプロジェクトの作成を終了します。

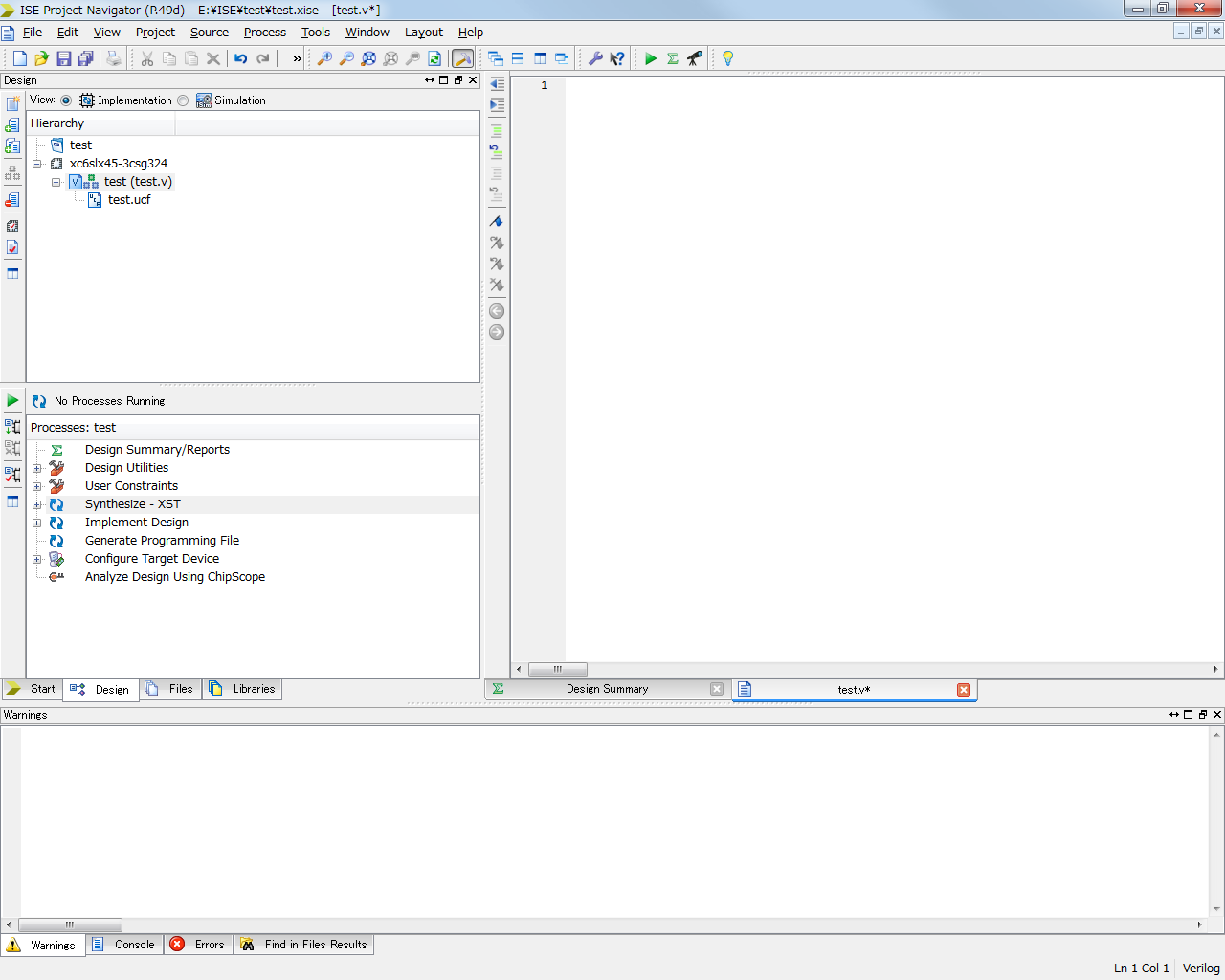

次に動作を記述するソースファイルを作成します。

メニューから[File]→[New]→[Text File]を選択すると空のファイルが作成されます。

空のファイルに以下のソースを入力して保存します。保存するときはverilogファイルの拡張子「.v」を選択します。

module test(

input CLK,

output LED

);

reg [26:0] count;

reg T1s;

reg toggle;

always@(posedge CLK)begin

if(count == 27'd99999999)

begin

count <= 27'd0;

T1s <= 1'b1;

end

else

begin

count <= count + 27'd1;

T1s <= 1'b0;

end

end

always@(posedge T1s)begin

toggle <= ~toggle;

end

assign LED = toggle;

endmodule

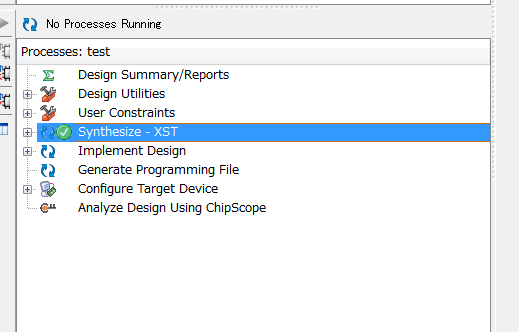

保存が完了したらProcessesペイン内の[Synthesize-XST]をダブルクリックして文法チェックを行います。

次に配線を記述するソースファイルを作成します。先ほどと同様に[File]→[New]→[Text File]を選択し、空のファイルを作成します。

空のファイルに以下のソースを入力して保存します。保存するときはucfファイルの拡張子「.ucf」を選択します。

このファイルは配線ファイルなのでボード特有のソースになります。ボードの仕様書を読んでソースコードの番号を変えてください。

(入力の水晶発振子と出力のLEDをFPGAから配線しています。)

NET "CLK" LOC = L15;

NET "LED" LOC = U18;

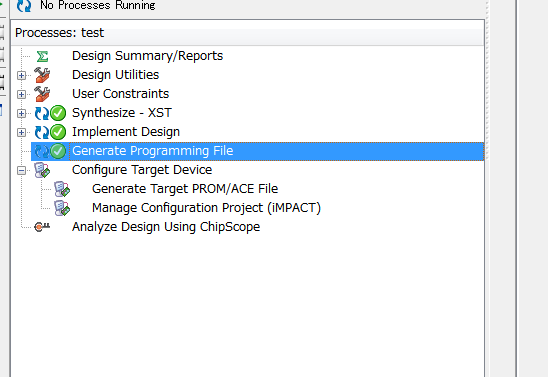

Processesペイン内の[Implement Design]をダブルクリックして配線チェックを行います。問題がなければ緑のチェックマークが付きます。

さらに[Generate Programming File]をダブルクリックしてFPGAに書き込むファイルを生成します。成功すれば緑のチェックマークが付きます。

最後はFPGAに書き込む作業です。

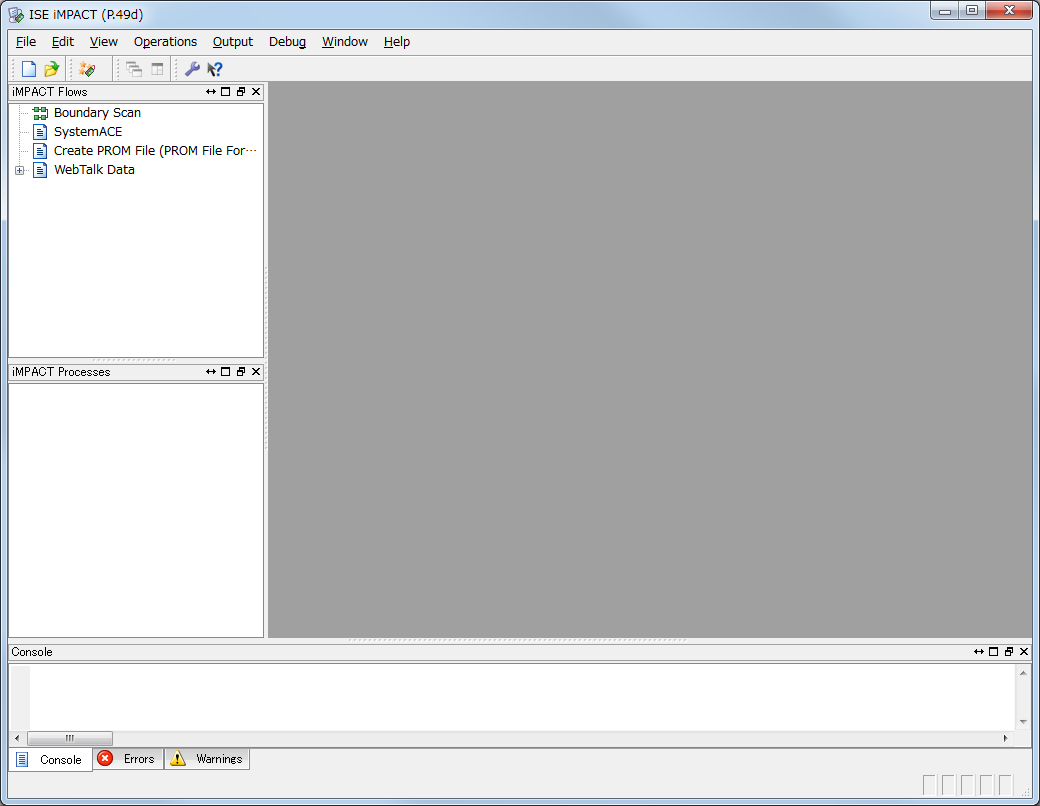

FPGAとパソコンを付属のUSBケーブルで接続してAtlysの電源を入れます。 接続したら左下の[configure Target Device]を開いて[Manage Configuration Project]をダブルクリックします。ISEiMPACTが起動します。

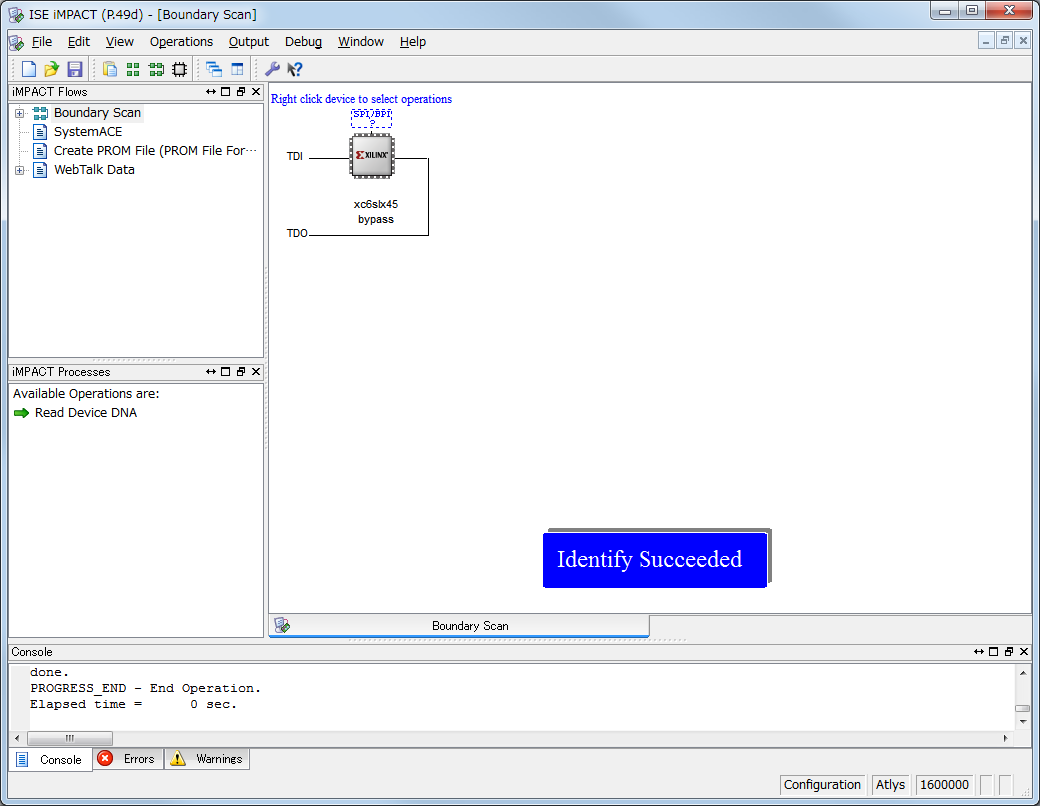

ウィンドウ左上のiMPACT Flowsペイン内の[Boundary Scan]をダブルクリックします。その後メニューから[File]→[Initialize Chain]を選択します。 これでデバイスとの接続が完了しました。

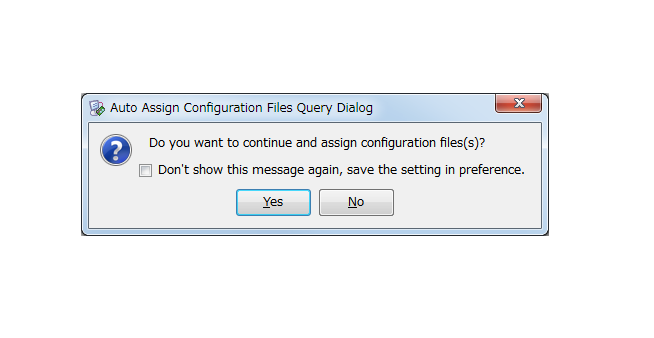

ダイアログが表示され、書き込むファイルの選択を聞いてくるので[Yes]を押します。

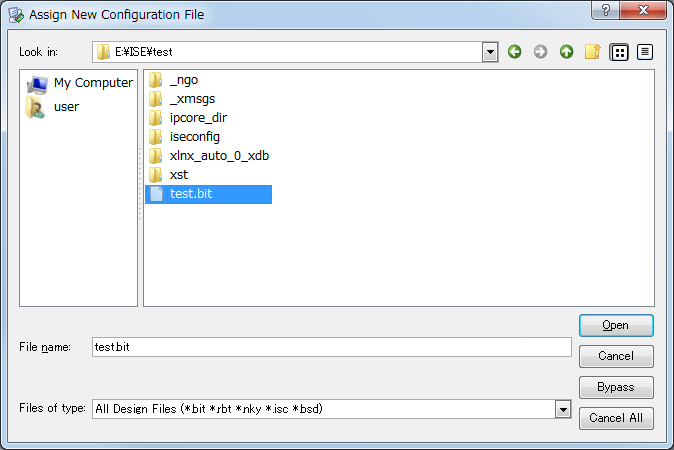

FPGAに書き込むファイルの選択します。[Generate Programming File]によって先ほどの プロジェクトの中に[.bit]という拡張子のファイルができているのでそのファイルを選択し、[open]を押します。

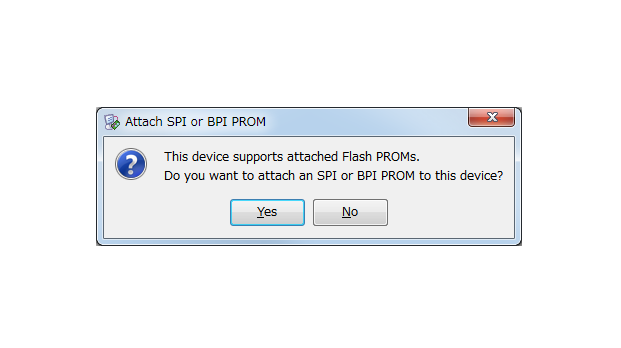

ダイアログが表示されPROMの搭載を確認してくるので[No]を押します。

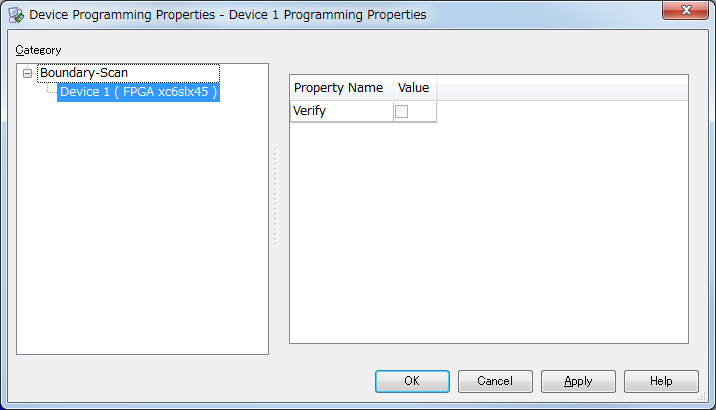

デバイスのプロパティが開かれるので[OK]を押して終了します。

最後にiMPACT Processesペイン内の[Program]をダブルクリックするとFPGAにプログラムが書き込まれ動き出します。1秒毎に消灯と点灯が切り替わっていれば成功です。 1秒毎になっていない場合は水晶発振子の周波数が違う可能性があります。

文法について

製作物にverilog-HDL簡易文法書があるのでもっといろいろ動かしてみたい人はそれを参考にしてみてください。